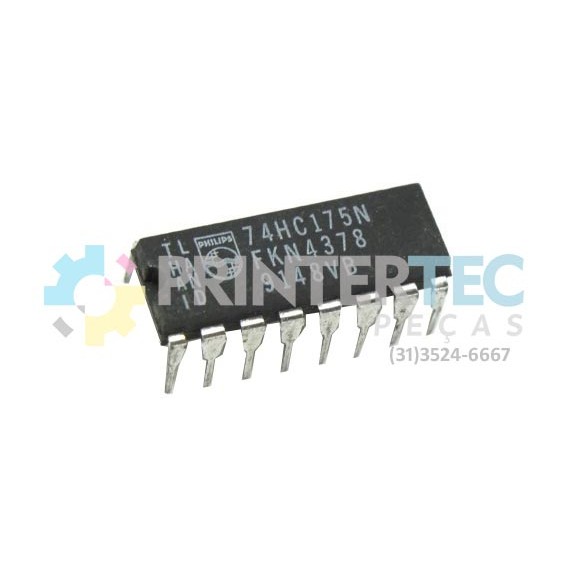

CIRCUITO INTEGRADO 74HC175N

D-Type Edge Triggered Flip-Flop

General description

The 74HC175, 74HCT175 are quad positive edge-triggered D-type flip-flops with

individual data inputs (Dn) and both Qn and Qn outputs. The common clock (CP) and

master reset (MR) inputs load and reset all flip-flops simultaneously. The D-input that

meets the set-up and hold time requirements on the LOW-to-HIGH clock transition is

stored in the flip-flop and appears at the Q output. A LOW on MR causes the flip-flops and

outputs to be reset LOW.

The device is useful for applications where both the true and complement outputs are

required and the clock and master reset are common to all storage elements.

Features and benefits

- Input levels:

- For 74HC175: CMOS level

- For 74HCT175: TTL level

- Four edge-triggered D-type flip-flops

- Asynchronous master reset

? Complies with JEDEC standard no. 7A

? ESD protection:

? HBM JESD22-A114F exceeds 2000 V

? MM JESD22-A115-A exceeds 200 V.

? Multiple package options

? Specified from ?40 ?C to +85 ?C and ?40 ?C to +125 ?C.

CIRCUITO INTEGRADO 74HC175N

D-Type Edge Triggered Flip-Flop

General description

The 74HC175, 74HCT175 are quad positive edge-triggered D-type flip-flops with

individual data inputs (Dn) and both Qn and Qn outputs. The common clock (CP) and

master reset (MR) inputs load and reset all flip-flops simultaneously. The D-input that

meets the set-up and hold time requirements on the LOW-to-HIGH clock transition is

stored in the flip-flop and appears at the Q output. A LOW on MR causes the flip-flops and

outputs to be reset LOW.

The device is useful for applications where both the true and complement outputs are

required and the clock and master reset are common to all storage elements.

Features and benefits

- Input levels:

- For 74HC175: CMOS level

- For 74HCT175: TTL level

- Four edge-triggered D-type flip-flops

- Asynchronous master reset

? Complies with JEDEC standard no. 7A

? ESD protection:

? HBM JESD22-A114F exceeds 2000 V

? MM JESD22-A115-A exceeds 200 V.

? Multiple package options

? Specified from ?40 ?C to +85 ?C and ?40 ?C to +125 ?C.